CPU er den utførende enhet i en datamaskin. Navnet, som er en forkortelse for Central Processing Unit, stammer fra den tiden det var bare én utførende enhet i en datamaskin. CPU som begrep brukes fortsatt, men det finnes mange typer og varianter. Prosessor eller mikroprosessor er ofte brukte synonymer.

CPU-en er den sentrale prosessorenheten i en datamaskin.

Virkemåte

CPU-en leser instruksjoner fra et program som ligger i arbeidslageret på datamaskinen og utfører dem én etter én. CPU har en programteller som inneholder adressen til den instruksjonen som skal utføres, og et antall andre registre. Et register har plass til et dataord. De vanligste instruksjonene gjør følgende:

- overfører data mellom register og arbeidslager (lesing og skriving)

- utfører aritmetiske og logiske operasjoner

- utfører testoperasjoner

Testoperasjonene har to utfall: fortsett med neste instruksjon eller hopp til adressen som er oppgitt i instruksjonen. Slik kan en få et program til å gå i løkke, det vil si å repetere en sekvens av operasjoner, eller velge alternative veier. Alle operasjoner i en CPU styres av en klokke, og en instruksjon tar et antall klokkesykler.

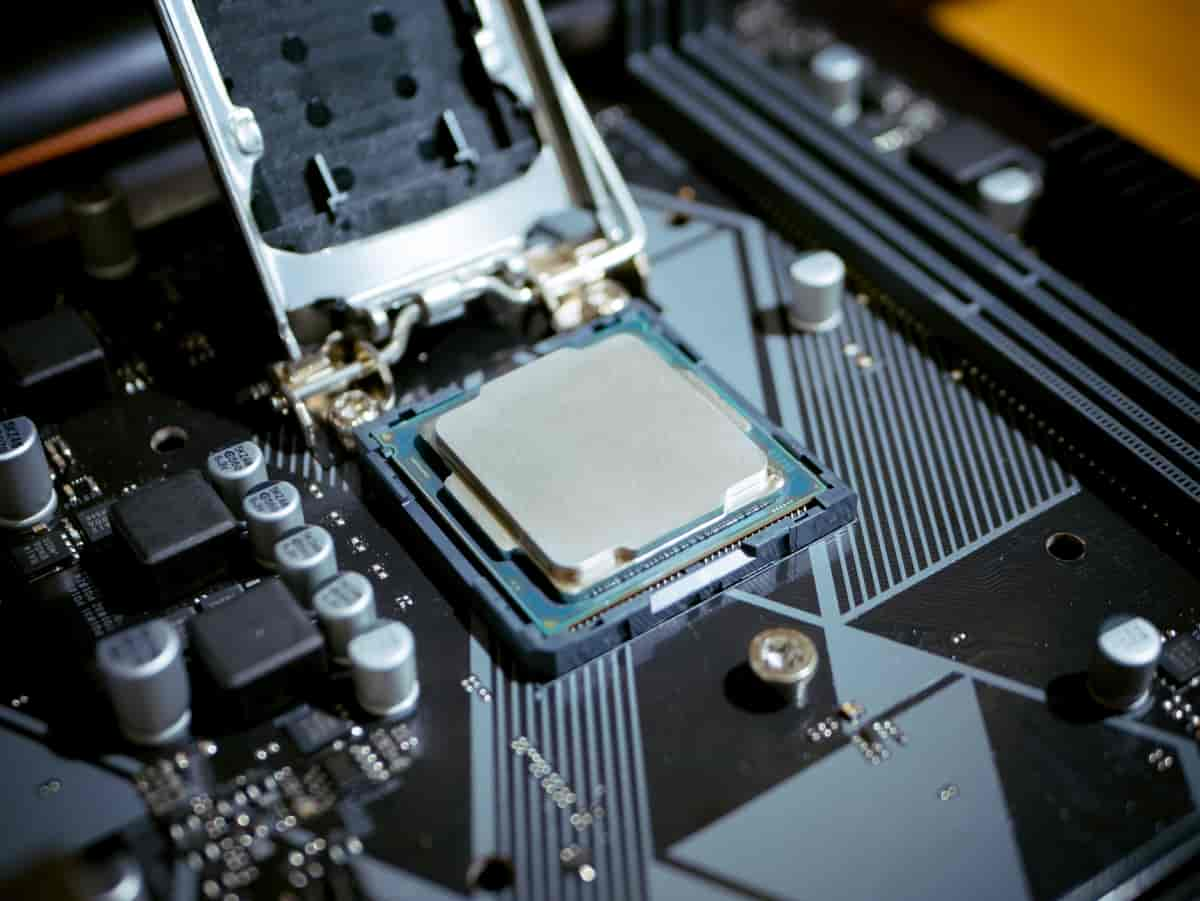

Konstruksjon

Før mikroprosessorene ble utviklet på 1980-tallet, ble CPU-ene bygget av diskrete elektroniske komponenter (brikker, chips) på kretskort (Printed Circuit Boards). Etter hvert kom det komplette CPU-er på én brikke.

En høy klokkefrekvens gir høy ytelse, men den kan ikke overstige det som kretsene i CPU-en tåler. Kretsene består av transistorer. En transistor har innstillingene av eller på, og omstillingen krever en viss tid som i dag måles i picosekund (en milliontedels milliontedels sekund eller 10–12 sekund). Transistorene blir raskere dess mindre de kan lages, men den store tettheten kan føre til at brikken blir for varm – selv med kjøling. Redusert klokkefrekvens vil redusere strømforbruket og dermed oppvarmingen, men vil også føre til redusert ytelse.

Moores lov sier at antall transistorer som økonomisk kan plasseres på en brikke dobles hver 24. måned. Økningen skyldes mindre linjebredder (mindre transistorer) som tillater økt klokkefrekvens, og at selve brikken blir større med plass for mer logikk og data – for eksempel cache. Større areal skyldes bedre produksjonsteknologi som gjør at en kan produsere større arealer med akseptabel feilrate. I praksis betyr Moores lov at en kan lage CPU-er med dobbel regnekraft etter 18 måneder.

Parallellprosessering

I stedet for å øke klokkefrekvensen har en de senere år satset på parallellprosessering. Først parallell utførelse av én instruksjonsstrøm, og da disse mulighetene var utnyttet: parallell utførelse av mange instruksjonsstrømmer. Vi får altså en CPU-brikke med mange CPU-er eller en flerkjernebrikke (multicore chip). Brikker med et lite antall kjerner; 2–20 er vanlig i dagens servere og PC-er (2020).

Når flere instruksjonsstrømmer utføres samtidig, fører det med seg flere kompliserende elementer. Operativsystemet må tilpasses. For å unngå omprogrammering kan et program bruke bare én prosessor om gangen. Parallellegenskapene blir utnyttet hvis en kan kjøre uavhengige programmer samtidig. Skal en sette mange prosessorer på samme oppgave må det nesten alltid foretas en betydelig omprogrammering.

Utførelse av instruksjoner

Programkoden ligger vanligvis lagret på disk. Instruksjonen som blir utført og tilhørende data som i øyeblikket blir behandlet må imidlertid ligge i arbeidslageret fordi det kun er der CPU-en kan hente instruksjoner og data. Maskinen må derfor kontinuerlig kopiere over relevante instruksjoner og data fra disk til arbeidslageret. Hvor i arbeidslageret programmet ligger, kan derfor variere for hver gang det blir utført. Det er avhengig av hvilke områder som er ledig. Det betyr også at de absolutte adressene til data og instruksjoner ikke er de samme når programmet lastes inn på et nytt sted. Disse problemene kan løses enten ved å bruke segmentregistre eller kravstyrt sidedeling.

Segmentregister

Segmentregistrene har to oppgaver:

- Tillate at alle programmer kan skrives som om de var lagret fra adresse 0.

- Stoppe programutførelsen og gi kontroll til operativsystemet hvis et program adresserer et dataord utenfor det området det er tildelt.

Segmentregisteret inneholder adressen til starten av et sammenhengende lagerområde der programmet er lest inn. Den virkelige (absolutte) adressen blir summen av verdien i segmentregisteret og instruksjonens adresse. Dette skjer automatisk for alle instruksjoner.

Sementregisteret inneholder også lengden på lagerområdet som programmet er tildelt. Utførelsen av programmet blir stoppet hvis det prøver å bruke en adresse utenfor området. Uten en slik mekanisme vil programmer kunne lese andres data og/eller ødelegge andre programmer bevisst eller utilsiktet. Dette er en helt fundamental sikkerhets- og beskyttelsesmekanisme. Ved avbrudd (engelsk: interrupt) hopper programmet til et bestemt program som rydder opp. Dette programmet er en del av operativsystemet.

Kravstyrt sidedeling

Ved kravstyrt sidedeling (engelsk: demand paging) deles programmet inn i blokker (pages) som normalt er 4 KB (4096 byte) store. Bare de mest aktive blokkene i øyeblikket blir tildelt plass i arbeidslageret. Hver blokk som har plass i arbeidslageret får 4096 byte sammenhengende lagerplass. Hvilke blokker av et program som faktisk har fysisk plass og hvor i arbeidslageret denne plassen starter står oppført i en blokktabell eller page table. Hvert program har sin egen blokktabell. For hver referanse til en adresse må i prinsippet et innslag i blokktabellen leses for å finne ut om blokken har fysisk plass og i så fall hvor blokken starter. Når den fysiske adressen er beregnet, vil den egentlige operasjonen til arbeidslageret bli utført. Hvis blokken ikke har en fysisk adresse, får programmet et avbrudd (interrupt) og operativsystemet må finne plass for den, samt lese den inn fra disk. Hvis blokken som viker plass er en datablokk som har fått endret sitt innhold, må den først skrives til disk før plassen kan frigis.

Sidedeling vil også fange opp referanser utenfor lovlig adresseområde på tilsvarende måte som ved bruk av segmentregistre. Sidedeling er en forholdsvis kompleks, men fleksibel mekanisme, og mange maskiner bruker denne mekanismen. For å utføre adresseomregningen hurtigere enn å lese i blokktabellen for hver referanse brukes en såkalt TLB – Translation Lookaside Buffer som inneholder de sist bruke adressene. TLB kan beskrives som en adresseberegningens cache.

Segmentering eller sidedeling

Ved sementering må en finne sammenhengende plass i arbeidslageret for hele programmet, eller de (få) segmentene som utgjør et program. Segmentene kan være store, de har også ulik størrelse, og det kan være vanskelig å finne sammenhengende plass i arbeidslageret for et segment uten å kaste ut andre segmenter. Programmer med minst ett segment ute av arbeidslageret får en pause i utførelsen.

Når en bruker sidedeling er alle blokker like store, noe som gjør det lettere å bytte plass. Bare de mest aktive delene av programmet trenger til enhver tid å ha plass i arbeidslageret, noe som gjør det mulig for mange programmer å være i arbeidslageret samtidig. Dette kan være positivt for å utnytte en flerkjerne-CPU.

Cache

For å redusere belastningen på buss og arbeidslager brukes cache. Når mange prosessorer bruker hver sin kopi av et dataord, må en sikre seg at alle enheter er enige om hva som er riktig verdi, det vil si at enhetene må ha et konsistent syn på innholdet av maskinens arbeidslager.

Dette kalles cache-konsistens, og kan realiseres på en rekke måter ved bruk av cache-koherens-teknikker. En enkel metode er å merke de andre kopiene som ugyldige når en kopi blir skrevet til. Det endrede ordet skrives umiddelbart til arbeidslageret. Hvis ordet skal brukes igjen, vil det bli hentet fra arbeidslageret og dermed er en sikret at siste kopi blir brukt også av de andre prosessorene.

Valg av instruksjonssett

Alle prosessorer har et definert sett av instruksjoner. RISC og CISC er betegnelser på filosofi for å utforme instruksjonssettet. RISC kommer fra Reduced Instruction Set Computer og CISC er det motsatte: Complex Instruction Set Computer.

CISC-instruksjoner blir utført av et mikroprogram; et fast program i kjernen av CPU. Det gjør det enklere å realisere et stort antall instruksjoner som gjerne kan være komplekse.

RISC-instruksjoner er få, og de blir utført direkte i elektronikken uten å gå veien om et mikroprogram. En RISC-instruksjon skal utføres hurtig, på få klokkesykler og med høy frekvens. Ulempen er at en trenger flere instruksjoner for å gjøre det samme som en kompleks CISC-instruksjon. RISC-fordelene er redusert ved at det etter hvert har blitt plass til mer elektronikk på en brikke, og således kan flere CISC-instruksjoner utføres direkte uten å gå veien om mikroprogram. Intels 86-arkitektur er CISC. ARM, PowerPC og SPARC er alle basert på en RISC-filosofi.

Spesialprosessorer

For tunge operasjoner som utføres ofte kan det være lønnsomt å lage spesialprosessorer eller akseleratorer. Eksempler på slike er signalbehandlingsprosessorer, grafikkprosessorer (GPU, Graphical Processing Unit), og kontrollere. Med utbredelsen av mobile enheter er det også viktig å lage CPU-er som bruker lite strøm.

Les mer i Store norske leksikon

Kommentarer

Kommentarer til artikkelen blir synlig for alle. Ikke skriv inn sensitive opplysninger, for eksempel helseopplysninger. Fagansvarlig eller redaktør svarer når de kan. Det kan ta tid før du får svar.

Du må være logget inn for å kommentere.